9. Detectores/generadores de paridad

Los circuitos electrónicos digitales se basan en la transmisión y el procesamiento de información, lo que hace necesario verificar que la información recibida es igual a la emitida; no suelen producirse errores, por lo que cuando ocurren en la mayoría de los casos el error en la transmisión se produce en un único bit.

El método más sencillo y eficaz de comprobación de la transmisión de datos consiste en añadir a la información transmitida un bit más, con la misión de que el número de 1 transmitidos en total sea par (paridad par), o impar (paridad impar).

Detectores/generadores de paridad

Los generadores de paridad par son aquellos circuitos que generan un 0 cuando el número de 1 en la entrada es par y un 1 cuando es impar, en el caso de dos bit, sería como se muestra en la tabla de verdad:

| Entradas | Salidas |

||

| A |

B | P | I |

| 0 | 0 | 0 | 1 |

| 0 |

1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

P = paridad par, es decir un número de 1 par.

I = paridad impar, es decir un número de 1 impar.

Las funciones canónicas serán:

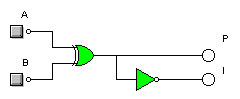

Cuya posible implementación se muestra en la figura:

|

| Imagen 28. Elaboración propia |

Como venimos comentando a lo largo de todo el tema

estos circuitos no se suelen cablear, sino que se presentan como circuitos

integrados, un ejemplo de generadores de paridad sería el CI 74180.